Fourth International Symposium on 3D Power Electronics:Integration and Manufacturing Florida International University, Miami, FL, February 2, 2023

# Heterogeneous Integration Roadmap

**Doug Hopkins** North Carolina State University DCHopkins@ncsu.edu

Integrated Power Electronics (IPE) Technical Working Group: Chapter 10

Patrick McCluskey University of Maryland mcclupa@umd.edu

### Integrated Power Electronics (IPE) Technical Working Group (TWG) 3D-PEIM

**Doug Hopkins**

North Carolina State University

DCHopkins@ncsu.edu

**Co-Chairs**

Patrick McCluskey University of Maryland mcclupa@umd.edu

PM Raj Florida International University mpulugur@fiu.edu

Cian Ó Mathúna Tyndall National Institute cian.omathuna@tyndall.ie

YY Tan **ON** Semiconductor

**Ray Fillion** Fillion Consulting fillion.consulting@gmail.com

**Brian Zahnstecher** Powerox

**Robert Davis** ON Semi Robert.Davis@onsemi.com

**Bob Conner Francesco Carobolante** X-Celeprint IoTissimo bconner@x-celeprint.com francesco@iotissimo.com

Slide 2

tan.yikyee@onsemi.com

**Jason Rouse** Taiyo

### Today is Groundhog Day

- Punxsutawney Phil saw his shadow and predicted 6 more weeks of winter

- Groundhog predictions have had a 39 % success rate

- Random guess has a 50% success rate

- We hope our Roadmap Predictions are better than the groundhog!

Slide 3

### Heterogeneous Integration of Power

The integration of separately manufactured power electronic components and subsystems into higher-level assemblies that provide enhanced functionality and improved operating characteristics.

Critical to: efficientl distribute clean power to multiple IPs requiring different voltages and currents

#### Efficiently - Reduce power loss so as to minimize need for cooling

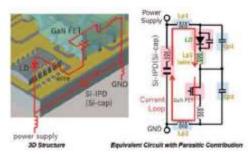

- Wide bandgap power devices that can operate at high frequency (e.g. GaN)

- New trace/via materials and shorter lengths to reduce interconnect/winding resistance

- Zero voltage, low capacitance, switching to reduce loss; lower core loss inductors

- Thermal isolation through glass and low k substrates, thermal metamaterials on layers

- Clean Minimize noise generated in the devices by power distribution

- Shielding, filtering, low permeability materials, reduced coupling, eddy currents low EMI

- Lower inductance through flip chip, Cu bumps, HDI, SiPLIT to lower  $\Delta I$  noise

- Decreased power path impedance

- Decoupling put power transmission on every interconnect level.

- Multiple Distribution to many different devices and device types

- Efficient scheme to minimize conversions to reduce losses

- Reduced size embeddable converters close to the devices being powered

- Multiphysics simulation, co-design and leverage AI

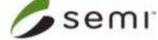

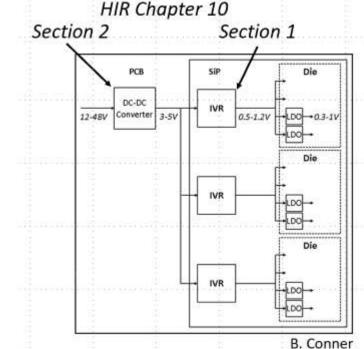

### **Heterogeneous Integration of Power Roadmap**

Heat sink

#### Latest update to HIR Chapter 10

- Section 1

- Section 2

- Section 3

- Section 4

#### **Integrated Power Electronics Components for**

- **Integrated voltage regulators** (IVRs) Up to 5V

- **Power System in Package Modules** 5-100V

- **Integrated High Power Systems** >100V

- **Energy Harvesting**

**INDUCTOR**

#### Agenda for each section:

- **Challenges** •

- **Metrics**

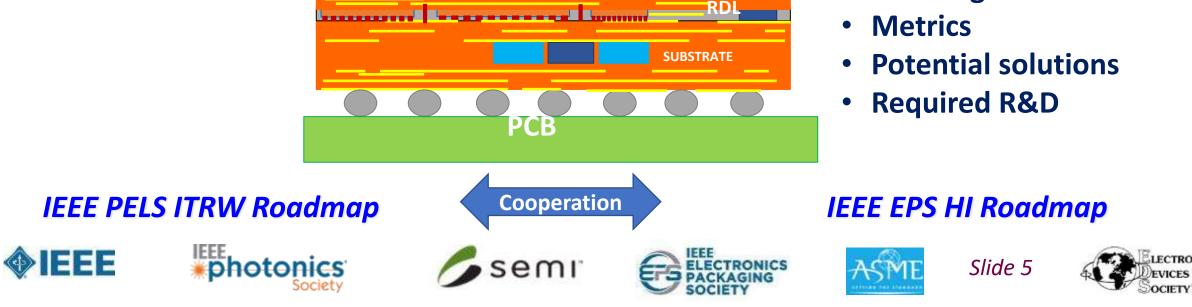

#### What is an Integrated Power Electronic Component (IPEC)

# **IPECs for Integrated Voltage Regulators (IVRs)**

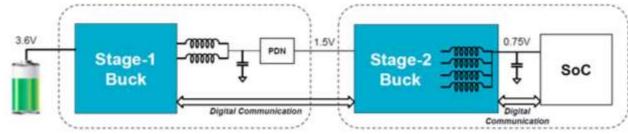

- Fine-grain power management significantly improves energy efficiency (performance-per-watt) by up to 73% by supplying the minimal voltage required at any given time to each load.

- It requires Integrated Voltage Regulators (IVRs) located in close proximity to the load to bypass the majority of the power distribution network (PDN) and associated impedance.

- PCB mounted voltage regulators (VRs) cannot supply accurate voltages due to their high PDN impedance.

- The way forward is PCB-mounted DC-DC converters that step down system bus voltage to an intermediate voltage, which is input to IVRs.

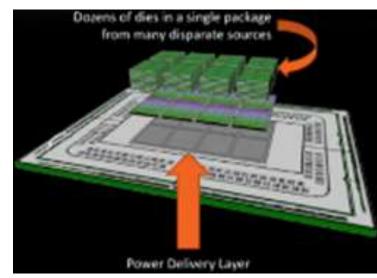

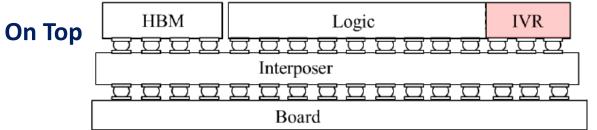

IVRs Integrated in SiP in Close Proximity to Loads

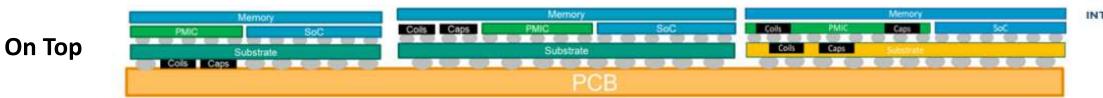

### Approaches to Heterogeneous Integration for IVR

- Disaggregate and tightly re-integrate separately manufactured components in a high reliability, low cost IPEC that provides multiple precisely regulated voltage outputs:

- Over a wide range of voltage (0.5 1.8V)

- With increasing input voltage (3-5V)

- At current density (10-20A/mm)

- And switching frequency (5-50MHz)

- With an ultrathin z-dimension (100 $\mu$ m or less).

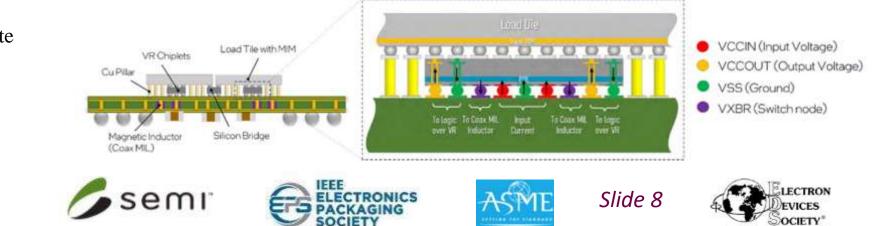

- Integrate IPECs in SiPs under the load die similar to silicon bridges, to provide vertical current flow for each voltage rail to its load from the PCB through the package substrate to the load die

- Minimizes lateral current flow and associated parasitics

- Significantly improves PDN and fine-grain power management.

- Capacitors may be integrated in the load die and/or the IPEC.

- Inductors may be integrated in the IPEC or package substrate

## **Metrics: IPECs for IVRs**

| Matuia                                      | Generation |         |        |         |  |  |

|---------------------------------------------|------------|---------|--------|---------|--|--|

| Metric                                      | 1          | 2       | 3      | 4       |  |  |

| Input voltage (V)                           | 3          | 3       | 5      | 5       |  |  |

| Switching Frequency (MHz)                   | 5 - 10     | 10 - 50 | 5 - 10 | 10 - 50 |  |  |

| Output current density (A/mm <sup>2</sup> ) | 10         | 20      | 10     | 20      |  |  |

| Output voltage (V)                          | 0.5 - 1.2  |         |        |         |  |  |

| Thickness (µm)                              | 100        |         |        |         |  |  |

Reduce routing loss Shrink passives, increase transient response Support many rails / phases Minimize power loss Ultra-thin for embedding in SiP

#### Plus:

- High efficiency

- Ultra-low thermal resistance

- High reliability

- Low cost

- Made with panel- vs. wafer-level processes

- High yield

- Known good die

- Modularity

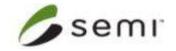

#### **How Are IPECs Integrated into SiPs?**

IPECs may be partitioned and integrated in multiple ways, each potentially serving different parts of hybrid topologies

### **IPEC Type A: Integrated in Load**

### **Monolithic Integration**

Power Transistors, Drivers, Controller

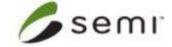

Package and Platform View of Intel's Full Integrated Voltage Regulators (FIVR)

#### **Hybrid Bonding**

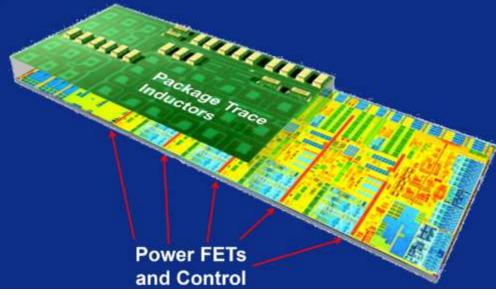

Integrate a hybrid converter topology:

- 1<sup>st</sup> stage: 48V-to-2V converter on landside of package

- 2<sup>nd</sup> stage: hybrid-bond deep trench capacitor (DTC) and

- integrated voltage regulator (IVR) layers to the processor dies

#### <u>IEEE Power Electronics Society October 22, 2020,</u> <u>Integrated Power – A Virtual Panel Session</u>

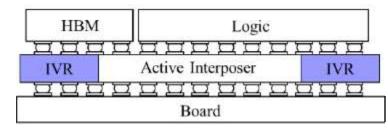

### **IPEC Type B: Integrated in Interposer**

Power Integrity Comparison of Off-chip, Oninterposer, On-chip Voltage Regulators in 2.5D/3D ICs

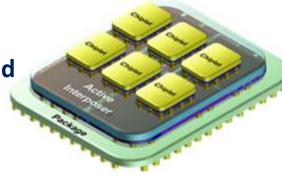

#### Monolithically Integrated in Active Interposer

From "CEA-Leti to Collaborate with Intel on 3D Packaging Technologies" A 220GOPS 96 Core Processor with 6 Chiplets 3D Stacked on an Active Interposer offers 0.6ns/mm Latency, 3Tb/s/mm<sup>2</sup> Inter-Chiplet Interconnects, and 156mW/mm<sup>2</sup>@ 82%-Peak-Efficiency DC-DC Converters

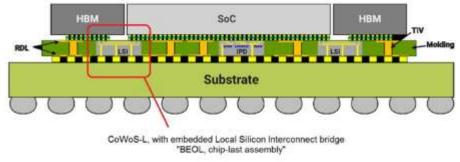

#### Embedded in Organic Interpower

Power Integrity Comparison of Off-chip, On-interposer, On-chip Voltage Regulators in 2.5D/3D ICs

TSMC Co-Wo-S-L

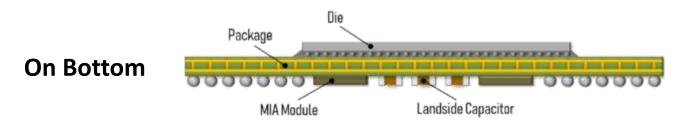

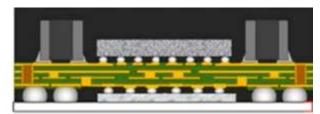

### IPEC Type C: Integrated in Substrate

Voltage Regulators with Integrated Inductors on Chip vs in Package

Magnetic Inductor Arrays for Intel<sup>®</sup> Fully Integrated Voltage Regulator (FIVR) on 10th generation Intel<sup>®</sup> Core<sup>™</sup> SoCs

- Monolithically integrate on processor die 1.8V MOSFETs, drivers and controllers for many buck regulators

- Magnetic inductor array (MIA) and capacitors on landside of package

- External PCB-mounted voltage regulators still required to supply 1.8V

**ASE's Double-Sided Mounting SiP**

|     | ••• • |

|-----|-------|

| *** |       |

|     |       |

| *** |       |

|     |       |

|     |       |

|     |       |

|     |       |

|     |       |

2020 11 18 IMAPS' webinar Enabling a Path to System Level Solutions

### Stand-alone SiP

Stand-alone on-board power SIP modules also play an important role in delivering power to most of the system components. They consist of switches, drivers and controllers, along with the storage elements such as passives. Use multi-level power conversion

Key Parameters include:

| Application             | Vin        | Vout                | Ι       | Efficiency           | di/dt | DVFS | Ripple |

|-------------------------|------------|---------------------|---------|----------------------|-------|------|--------|

| Server processor        | 12-48 V    | ~1 V                | ~100 A  | High at high current | High  | Low  | Medium |

| Graphic processor       | 12-48 V    | ~1 V                | 100's A | High at high current | Low   | Low  | Medium |

| AI accelerator          | 12-48 V    | ~1 V                | 100's A | High at high current | Low   | Low  | Medium |

| Mobile processor        | 2.3-5 V    | ~0.4-0.8 V          | ~5 A    | High 10 mA to 3A     | High  | High | Medium |

| HBM Module              | 3.3-5-12 V | ~1 V                | ~10 A   | High at high current | Low   | Low  | Medium |

| Optical module          | 3.3 V      | ~0.4 <b>-</b> 0.8 V | ~10 A   | High at high current | Low   | Low  | Small  |

| Cell Baseband processor | 5-12 V     | ~1 V                | ~5-20 A | High at high current | Low   | Low  | Small  |

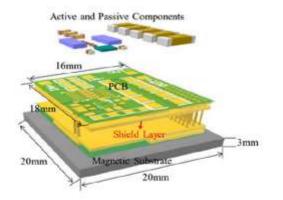

### SiP Power Module Advancements Needed

- Increased volumetric density of passives without sacrificing efficiency & power handling.

- High Tg (>250°C) substrates with low moisture absorption, resistance to electrochemical migration at high temperature and humidity.

- Devices with copper termination

- Backside metallization of dies compatible with direct bonding on copper leadframes or packages.

- Pressureless assembly of dies with nanosilver and nanocopper.

D-PEI

HETEROGENEOUS

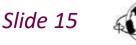

### Need for Embedded Power Passives

### Capacitor Technologies

|                       | Thin MLCC                   | Trench Caps           | Ta Chip         | Emerging Need                                  | INT     |

|-----------------------|-----------------------------|-----------------------|-----------------|------------------------------------------------|---------|

| Volumetric<br>Density | 20 µF/mm <sup>3</sup>       | 10 μF/mm <sup>3</sup> | ~10 μF/mm³      | 50-100 μF/mm <sup>3</sup>                      |         |

| Thickness             | 100 µm                      | 100 µm                | 600 µm          | 50-100 μm                                      |         |

| Freq.<br>Stability    | 10-100 MHz                  | >1-10 MHz             | 0.2 -1 MHz      | >10 MHz                                        |         |

| ESR                   | ~10 mΩ                      | 50 mΩ x μF            | >100 mΩ x<br>μF | ~50 mΩ x μF                                    | B - 13  |

| % ΔC/V                | -13 % to -70%<br>(1 to 4 V) | ~ 0 %                 | ~ 0 %           | ~ 0 %                                          |         |

| Max. Temp             | 85° C                       | 150° C                | 125° C          | >125° C                                        |         |

|                       | PICK AND PLACE              |                       |                 | FILM EMBEDDING WAFER OR<br>PANEL INTERCONNECTS | <u></u> |

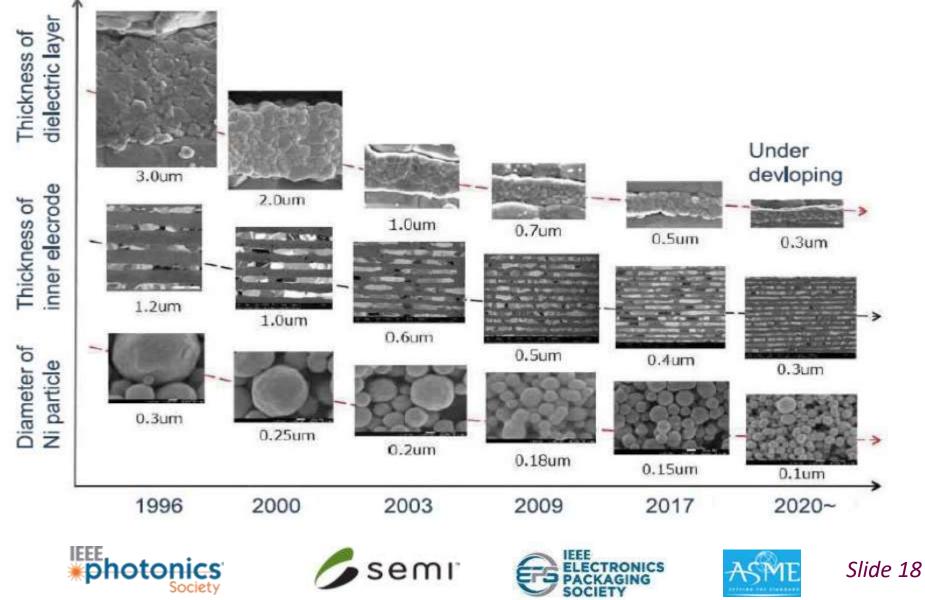

### MLCC Evolution [Murata]

**ØIEEE**

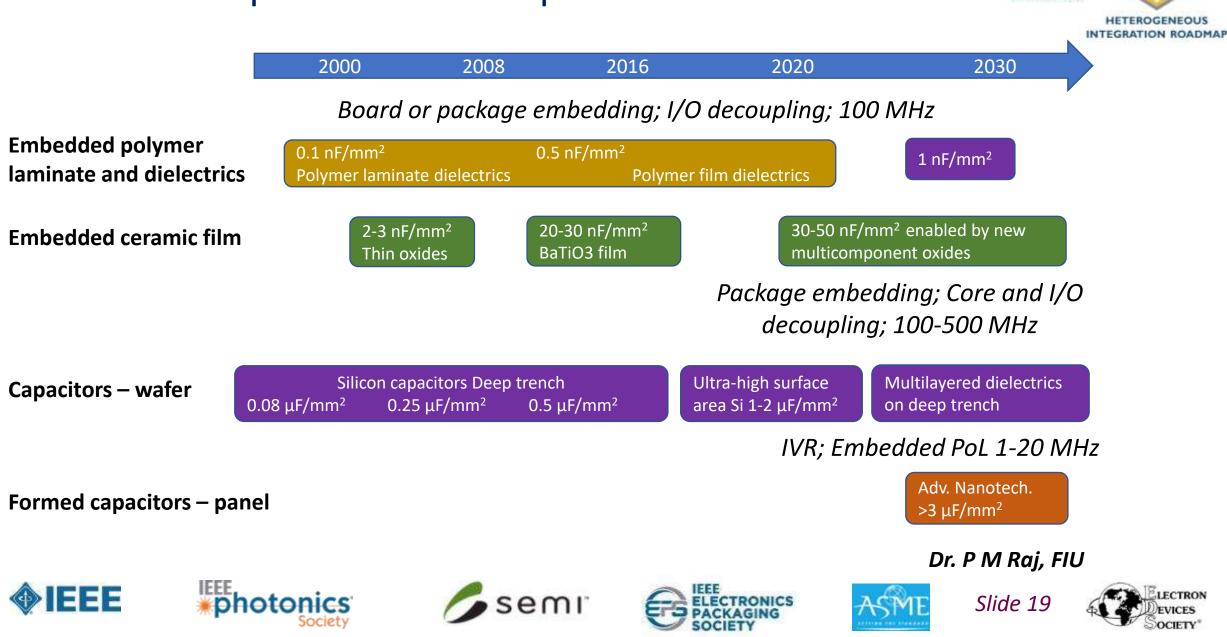

### **Embedded Capacitors Roadmap**

3D-PEIN

### Inductor Technologies

|                                      |                                            |                                                              | 1                                                                                      |                        | HETEROGENEOUS       |

|--------------------------------------|--------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------|---------------------|

|                                      | Discrete (Ferrite or<br>Metal Powder)      | Magnetic composites –<br>substrate-embedding                 | Nanomagnetic films:<br>On-chip                                                         | Need                   | INTEGRATION ROADMAP |

| L (nH)/R <sub>DC</sub> (m $\Omega$ ) | 15-25                                      | 5-10                                                         | 0.1-0.2                                                                                | >>10                   |                     |

| Q                                    | >20                                        | <10                                                          | 5                                                                                      | >20                    |                     |

| Current (A/mm <sup>2</sup> )         | 0.01 - 0.1                                 | 0.1 - 1                                                      | 5-10 A/mm <sup>2</sup>                                                                 | 5-10 A/mm <sup>2</sup> |                     |

| Thickness                            | 200- 500 μm                                | 50 - 200 μm                                                  | 25 µm                                                                                  | 25-50 μm core          |                     |

| Cost                                 | Low                                        | Low                                                          | High                                                                                   | Low                    |                     |

|                                      | Discrete - Example<br>(0.5 x 0.1 x 0.5 mm) | <sup>10μm</sup><br>KEMET-<br>Tokin                           | Declearies Magnetic<br>Lamination<br>Insulating<br>Layer<br>Layer<br>102280028 Gaerial |                        |                     |

|                                      |                                            | Cooper venuelors                                             | Silicon                                                                                |                        |                     |

|                                      | Qualcomm PMD9645 PMIC                      | Substrate-embedded inductors<br>Magnetic Core (0.5 - 0.6 mm) | Intel and Ferric                                                                       |                        | P M Raj, FIU        |

| IEEE 🐇                               | photonics<br>Society                       | /semi 🔂                                                      |                                                                                        | TE Slide 20            |                     |

### Magnetic Material Options

E

LECTRON

|                                         | Thickness<br>Microns | Coercivity<br>A/m | Resistivity<br>μ Ohm cm | Saturation<br>Flux (Tesla) | Permeability |

|-----------------------------------------|----------------------|-------------------|-------------------------|----------------------------|--------------|

| Mn,Zn ferrites                          | >100                 | 3-5               | 10,000                  | 0.6                        | 5000         |

| Nanocrystalline and<br>amorphous flakes | >15                  | 3                 | 110                     | 1.2                        | 15000        |

|                                         |                      | 0.1 – 5 M         | Hz                      |                            |              |

| Electroless thinfilms                   | 3-5                  | 10-20             | 100                     | 1                          | <<1000       |

| Plated thin films                       | 2-100                | 20-80             | 35                      | 1.3                        | ~1000        |

| lake composites                         | 25-500               | 100-200           | 10,000                  | 0.8                        | 100-150      |

|                                         |                      | 1 – 10 N          | 1Hz                     |                            |              |

| Nanomagnetic films                      | 1-10                 | 10                | 200-300                 | 1.5                        | 200-500      |

|                                         |                      | 10 – 150          | MHz                     |                            |              |

|                                         | ety 2                | semi              | ELEC<br>PACK<br>SOCI    |                            | SME Slide 2  |

### **Integrated Inductors**

- Small footprint (0201 0.2mm x 0.1mm) discrete inductors, using high frequency (100MHz+) polymer loaded composites or fired magnetic material. Surface-mount devices [Murata] or with copper terminations, embedded in the SOC organic substrate or package [Taiyo Yuden].

- High frequency ferrite cores embedded in 2.5D/3D heterogeneous integration structure using BEOL interconnect processing to provide windings [IMEC].

- Vertical coaxial magnetic composite core inductors integrated in the package substrate [Intel].

- Embedded magnetic-on-silicon inductors embedded in PCB substrate or package [Wurth].

- Embedded thin film CZT combined with copper windings in PCB substrate or package [Tyndall].

- Electroplated planar copper windings with electro-deposited magnetic core [Enachip].

- Vertical inductors based on thin film CZT deposited on the sidewalls of low-profile electroplated copper pillars [Tyndall].

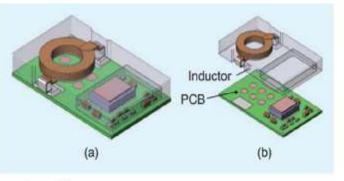

### **Embedded Inductors in Power Modules**

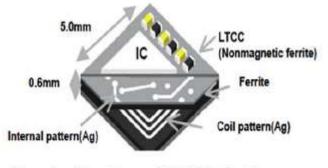

Murata, Ferrite and LTCC Inductor substrates

Sumida (Inductors in lead-frame molding)

Modules on silicon capacitor substrates; Murata's LIDAR modules

(a) Single phase

(b) Two phase coupled

Virginia Tech (Inductors in laminate)

GaN DC-DC converter with substratesembedded inductors

### Key R&D for IVR Inductors

- Requires considerations of 3D inductor design, magnetic material synthesis and processing, integration and assembly into packages, substrates and interposers.

- Increasing DC nH/mOhm beyond 1.0 (up to 5.0 to 10.0).

- For magnetic core solutions, increasing the saturation current up to 5 to 10 A DC.

- Exploiting the vertical direction to provide reduced footprint, ultra-low dc resistance inductors to produce a useful, single vertical inductor.

- Exploring integrated inductor arrays in interposers or substrates for complex granular power architectures.

- Considering the EMI implications of integrated inductors and appropriate solutions.

- Utilizing the "parasitic inductances" within the system architecture, either with or without magnetic material enhancements.

### **R&D** Needs for Passives

|            |                     |                                                                                                    | 21 |

|------------|---------------------|----------------------------------------------------------------------------------------------------|----|

| Capacitors | Density             | High K dielectrics;<br>Enhance electrode surface area;<br>New dielectrics and deposition processes |    |

|            | Frequency stability | Electrodes and connectivity with lower parasitics                                                  |    |

|            | Integration         | Thinner form-factors;<br>Substrate or wafer or fan-out embedding                                   |    |

| Inductors                     | Density              | Higher permeability with saturation field and high resistivity                |

|-------------------------------|----------------------|-------------------------------------------------------------------------------|

|                               | Efficiency           | Low coil DC losses ;<br>Low core losses with low coercivity and eddy currents |

| L <sub>1</sub> L <sub>2</sub> | Integration          | Substrate- or wafer-compatible process                                        |

|                               | Current-<br>handling | Design innovations;<br>Scalability in thickness to handle higher current      |

Slide 25

# Integrated Power Electronics Technical Working Group

### **Many Thanks For Your Attention**

*If interested in joining our IPE-TWG please contact any of our members.*