# Enabling Sustainable Power Electronics Through Miniaturization and Integration of Power Magnetics

**Matt Wilkowski**

**VP Engineering & Magnetics – EnaChip Inc.**

# **Electrification - Autonomy**

### The Problem:

**World needs**

**MORE power in SMALLER spaces:**

**High Power Density**

#### **Computing**

3 million transistors

7 billion transistors

#### **Advanced Health**

# **Breaking Down the Problem**

- New megatrends like AI, and the age of "Everything Connected" continue to drive <u>power</u> needs for higher performance computing, mobility, connectivity and autonomy.

- Electronic devices and applications continue to push the boundaries of size smaller and more compact form factors, ultra-high speed data transmission, and improved energy efficiency.

- Proposed solutions must feature the <u>ease of design</u>, integration into an existing ecosystem and minimal re-learning for developers.

- Legacy technologies are not enough!

these multitudes of new and emerging applications require a re-imagined solution space for design of electronic devices including microchip power solutions

size

weight

and

performance

cost

THE ROOT CAUSE of POWER INEFFICIENCIES

Power

Is Separate From

Silicon

### Required Fundamental Magnetics Solution

Leading edge magnetic materials and device designs to provide a **solution space that is a customizable convergence of performance and desired form factors** for even the most demanding electronic applications in computing, mobility, power and sensing.

#### **Basic ingredients include:**

- Low cost of implementation

- Ecosystem in place

- Seamlessly <u>Integratable</u> into market driven devices

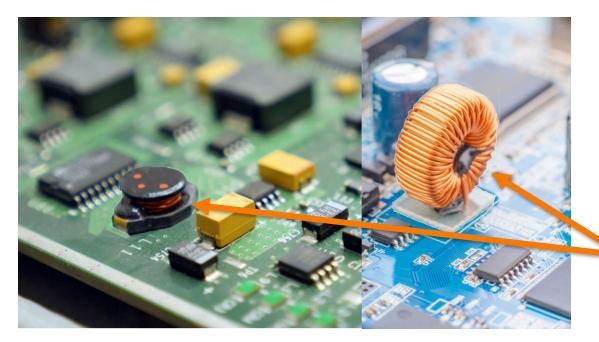

# INTEGRATION ROADBLOCK

Discrete power magnetics (e.g., Inductors and transformers) are the largest components on the board!

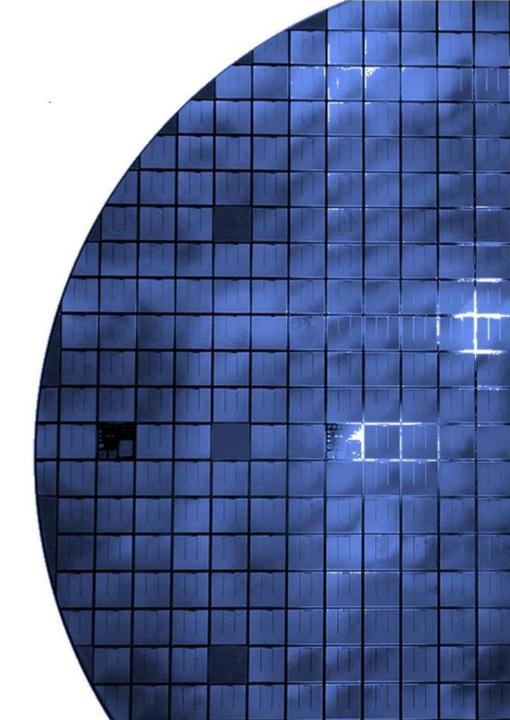

# Wafer Level Magnetics Integration will make them invisible!

### **Goals of Magnetics Integration**

Meet cost – manufacturing and packaging

Meet form factor – footprint and thickness

Meet quality and reliability

Meet performance - electrical I<sub>SAT</sub> - L - DCR - Q (Power Loss)

The intangibles – near field noise, thermals, integration compatibility

Wafer Level Magnetics is a viable option to meet these goals

EnaChip Inc. presented at 3D PEIM 2023

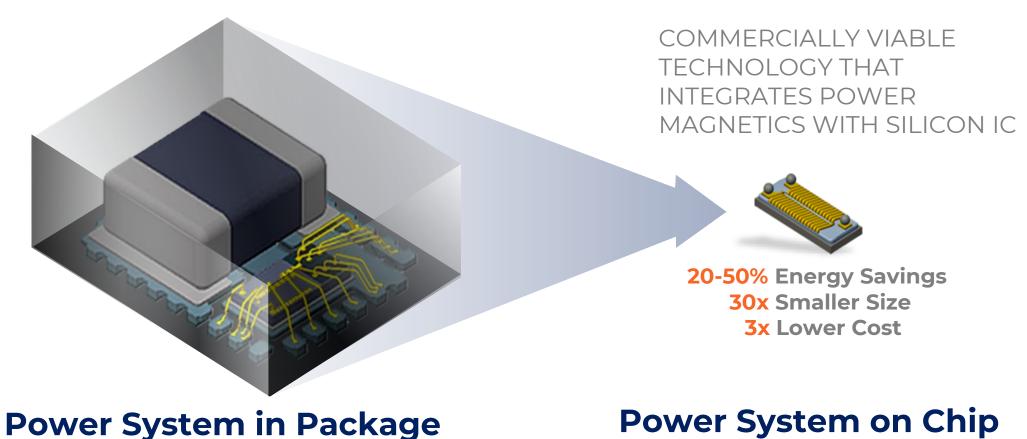

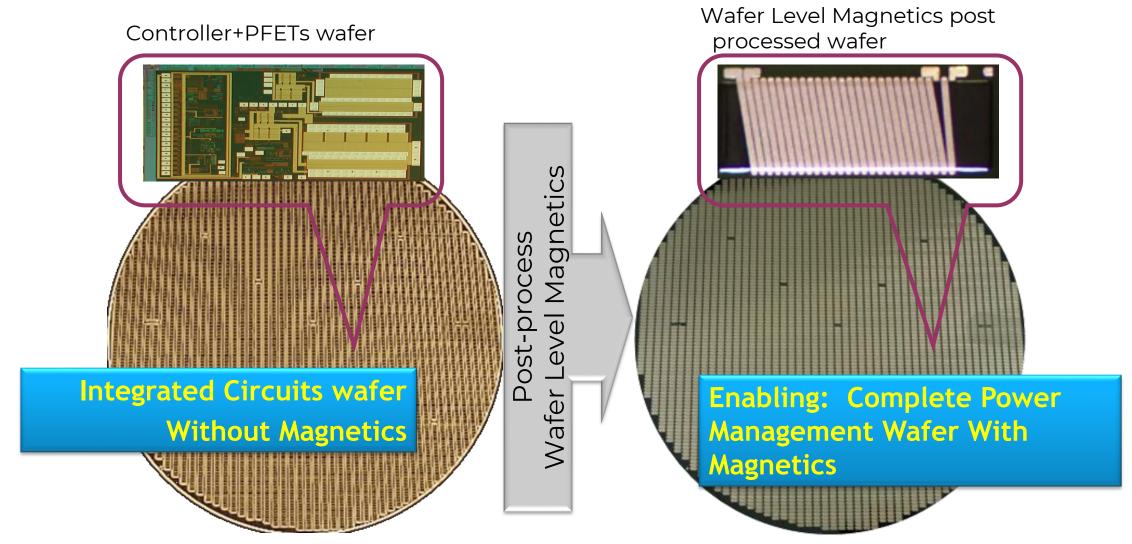

# Wafer Level Magnetics Next Step For Innovation in Integration

**Power System on Chip**

**EnaChip Enabled Solution**

# Wafer Level Magnetics (Core technology options)

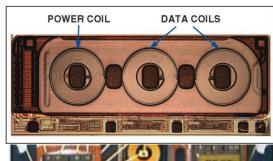

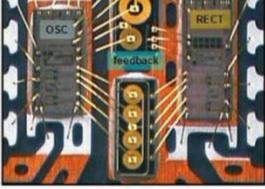

#### **Aircore WLM**

iCoupler, ADI

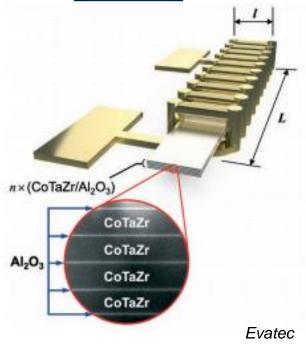

#### Multilayered thick film sputtered core

Multilayered thick film electroplated core

**Enpirion**

Electroplating windings

Electroplating windings

Electroplating windings

# **Wafer Level Magnetics**

(Core technology comparison)

#### **Aircore WLM**

- Easy to fabricate

- Low cost

- Low power loss

- High near magnetic fields

- Low inductance

- Requires high F<sub>sw</sub>

# Multilayered thick film sputtered core

- High performance

- Process/thickness control

- FEOL compatible

- ♣ Slow (0.1um/min)

- High cost process(~10-20x of the plating)

- High capital costs(>5X over electroplating)

- Thickness/Stress limitations (<20L, <3 um)</p>

Power ≈ core thickness

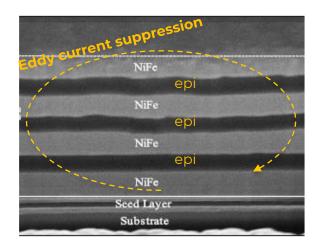

# Multilayer thick film <u>electroplated</u> core

- Fast deposition (1um/min)

- Low cost process

- Intrinsically low stress→ No. layers (>100)

- Low capital costs (BEOL-OSAT)

- Highly scalable

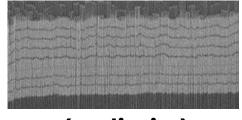

- Metallic high µ crystalline films have low p→ small skin depth → higher loss

- Multi-layer laminations needed for high currents >1A

Complex multi-layer/multi-mask **cost prohibited process**

# **Enachip's Technology Platform**

Enachip addresses the electroplating core shortcomings to enable a high performance WLM cost competitive solution

#### **Electroplating core**

- Fast deposition process (1mm/min)

- Low-cost process

- Intrinsically low stress → No. layers (>100)

- Low capital costs (BEOL OSAT)

- Highly scalable

- Metallic high μ crystalline films have low ρ→ small skin depth → higher loss

- Multi-layer laminations needed for high currents >1A

Complex multi-layer/multi-mask cost prohibited process

## **EnaChip** Creates an Enabling Technology Platform

Innovative

wafer fabrication processes

Unique high-performance magnetic materials

silicon based control circuits (node independent)

#### Multiple Addressable Market Verticals

#### **Current Roadmap Focus**

#### **Power Management**

DC/DC Voltage Regulators PMIC LED Drivers

#### **Signal Conditioning**

Filters Tuners

#### Intelligent Sensors - Automotive and IoT

- Current sensing

- Magnetic Field Sensing

#### **Connected and Smart Health**

- Electromagnetic Separation

- Micro-pumps, micro valves, relays

#### **Microdevices**

Electromagnetic Actuators Power Harvesting Switches

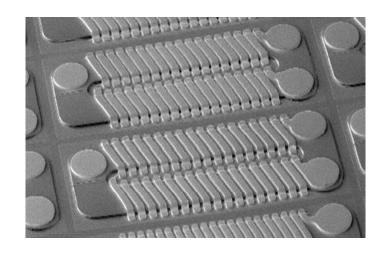

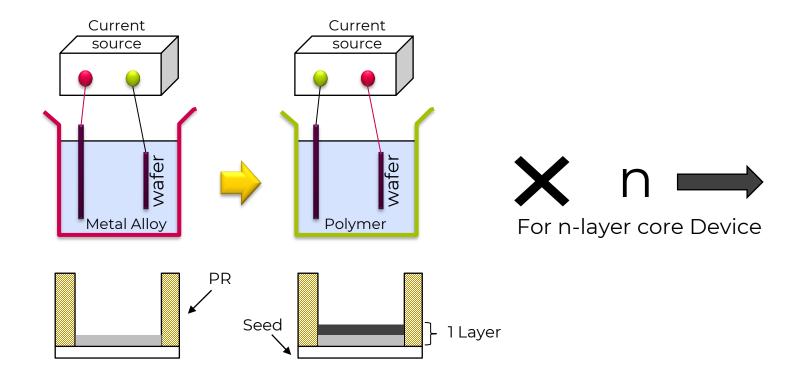

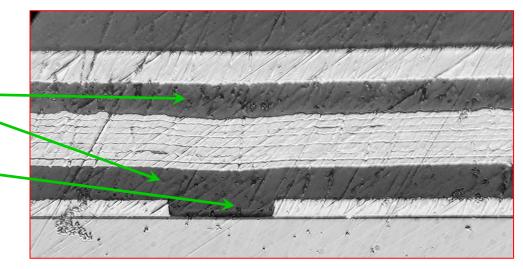

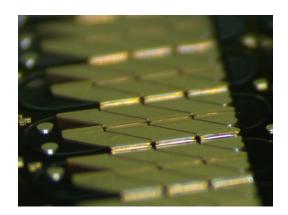

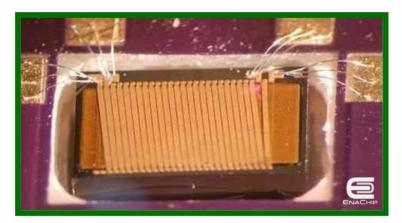

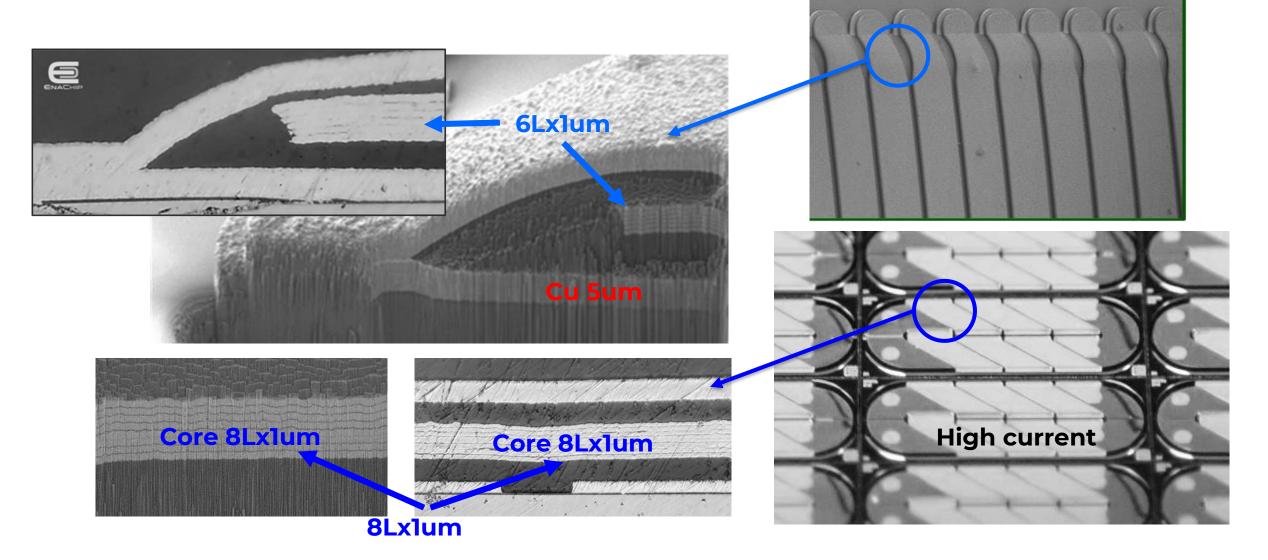

# Key Process Modules (Electroplated micro-coils)

- Thick electroplated Cu (5um 80um)

- Dielectric insulation/planarization

- Electroplated high frequency magnetic alloy laminations

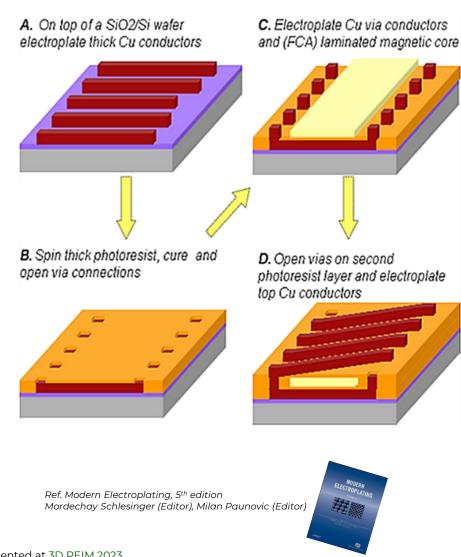

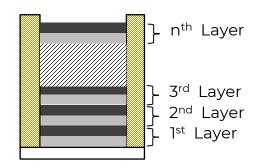

# **Game Changing Cost Reduction!**

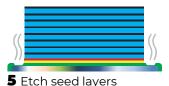

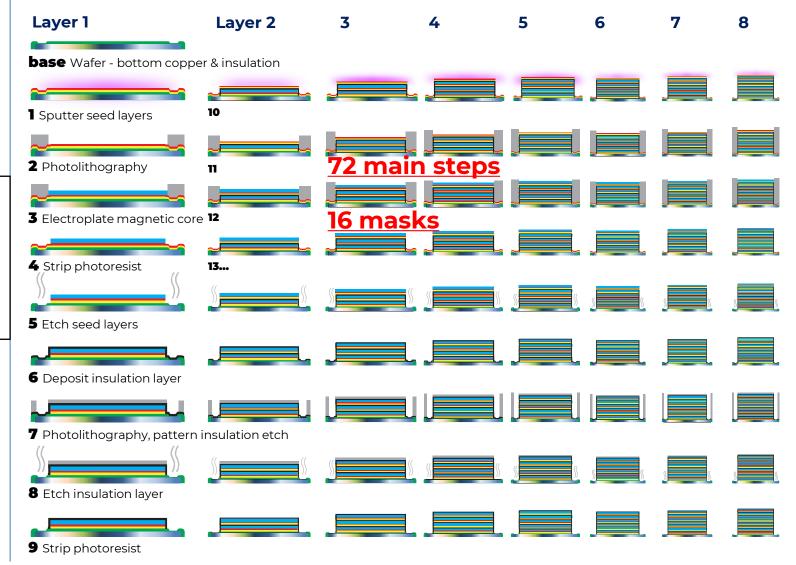

EnaChip process for 8 core layers Using electroplated EPI as insulator

base Wafer - bottom copper & insulation

1 Sputter Seed Layer

5 main steps

1 mask

2 Thick photolithography

**3** Sequentially electroplate 8 layers of magnetic core and insulation

4 Strip photoresist

<u>Today's</u> process for 8 core layers using **sputtered SiO<sub>2</sub>** as insulation

# **Electroplating's Competitive Advantage**

#### **Sputtered Laminated Cores**

- High Cost

- Slow process

- Foundry node bound

Microtransformer (2.6mm x 2.4mm)

**20L TOTAL 4.5um**

Deposition time 1.6 days!

(up to 5um)

#### **Continuously Electroplated Laminated Cores**

- Simple process

- Ultra Low Cost

- Ultra fast process

- On Any wafer, Any Node!

**8L TOTAL 8um**

Deposition time 1.2 hours!

(no limits)

### The advantage of being... Node-Agnostic

(EnaChip's "Magnetic Functionality" can be post-processed on ANY substrate from ANY foundry and ANY node!)

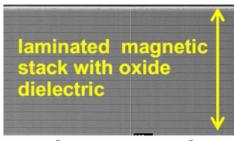

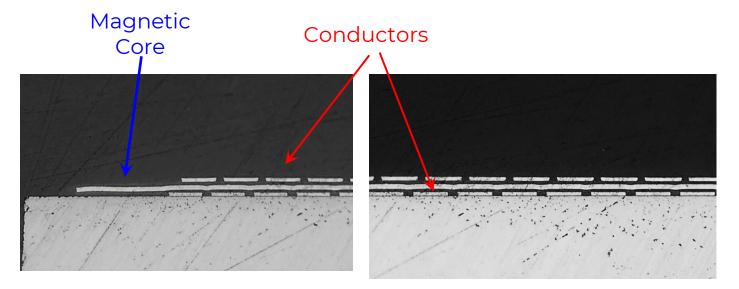

# Multi Layer Process Incorporates Electro Plated Insulator (EPI)

ENACHIP

- Electrochemically synthesized insulator

- Conjugated polymer based

- Conductivity < 1S/m</p>

### Photolithographically definable dielectric

- Photosensitive cured polymer as dielectric

- Between magnetic stack and conductors

- Between conductors

- Dielectric Constant ~ 4

- Breakdown Voltage > 600 V/mm

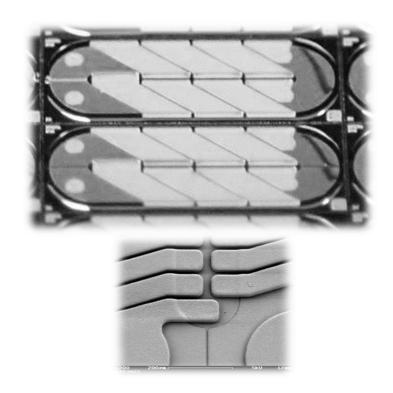

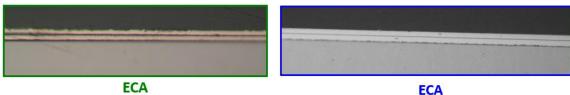

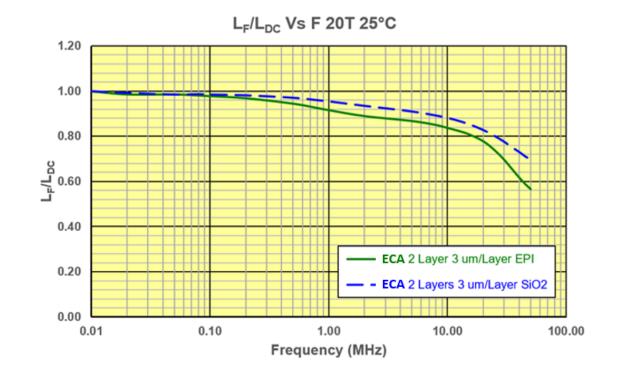

# EnaChip's Electro-Plated Insulation "EPI" (Performance comparison of EPI vs. SiO<sub>2</sub> as lamination insulator)

2 Layers 3 um/Layer EPI Between Layers

2 Layers 3 um/Layer SiO<sub>2</sub> Between Layers

Test donuts are made of 2 Layers of magnetic material separated by EPI and SiO2 for comparison

- Donut-0 ID=6mm OD=19mm

- Closed magnetic path

EPI insulation is as good as SiO2 insulation

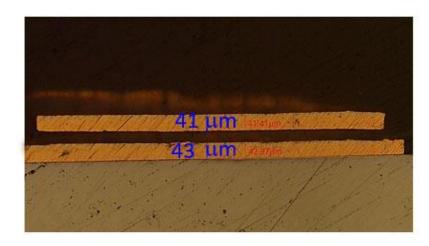

### Thick (> 40 μm) Copper

ENACHIP

- Thick copper enables lower DCR per turn

- For a given DC power loss budget

- Lower DCR per turn enables more turns

- More turns enables higher value of inductance

- More turns enables higher volt-second capability

- Higher values of inductance and volt second capability

- Enable higher input voltage buses beyond 3.3V, 5V, 12V towards 18V/24V

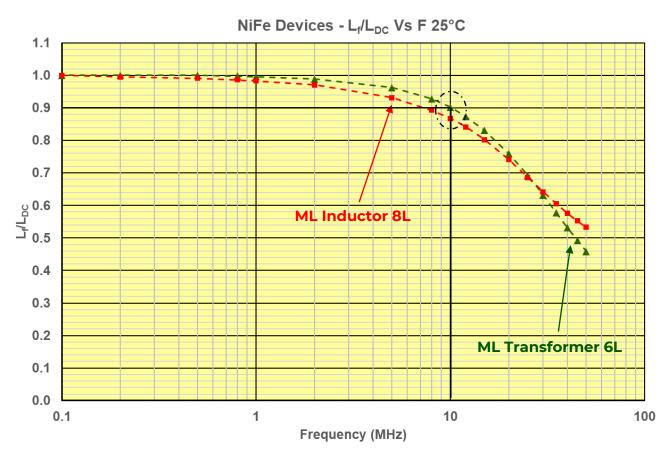

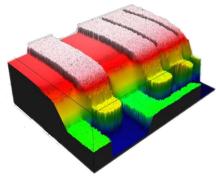

# Device Performance Using Mag Core with Single Mask n-Layer process

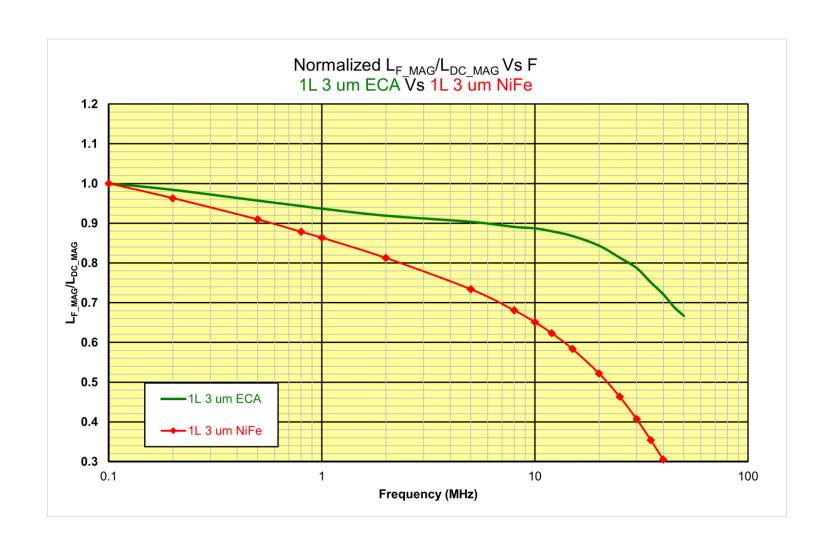

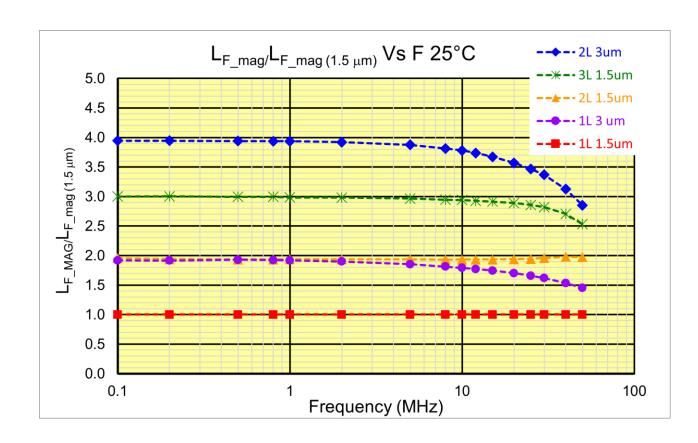

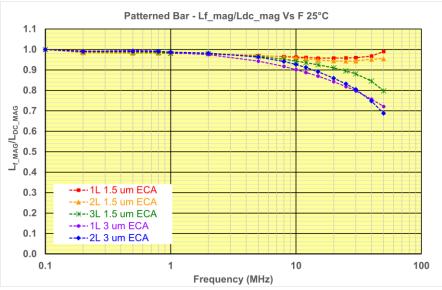

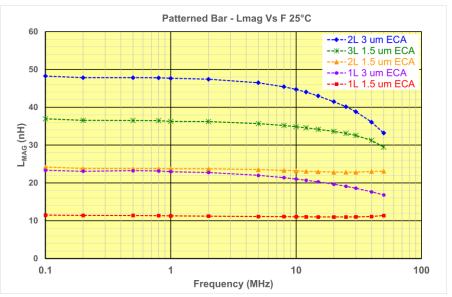

EnaChip multilayer lamination process extends the performance of NiFe materials to maintain higher values of inductance at higher frequencies.

L=20-40nH die 2mm x 5mm

L=120-150nH die 1.7mm x 4.0mm

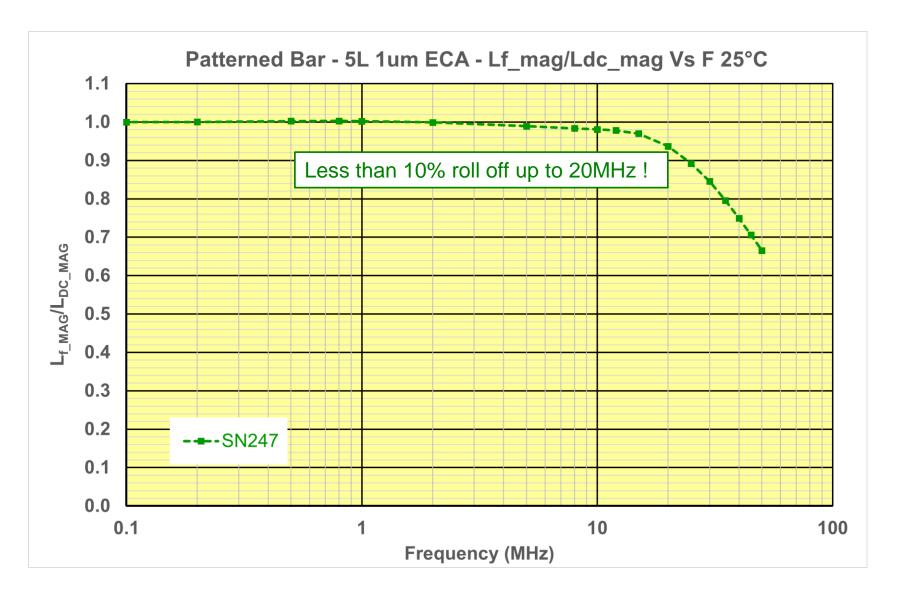

# Multi Layer ECA – High Frequency Performance

### **Device Structure**

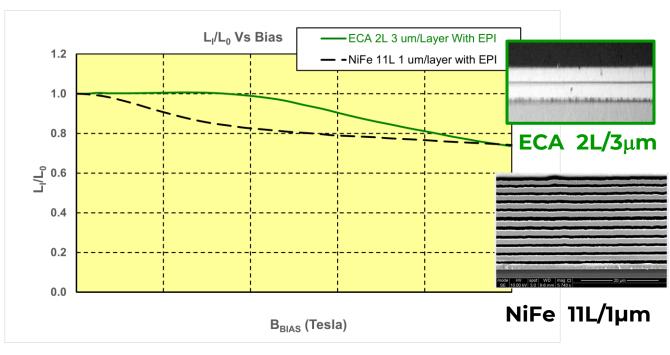

# EnaChip's alloy ECA vs. NiFe

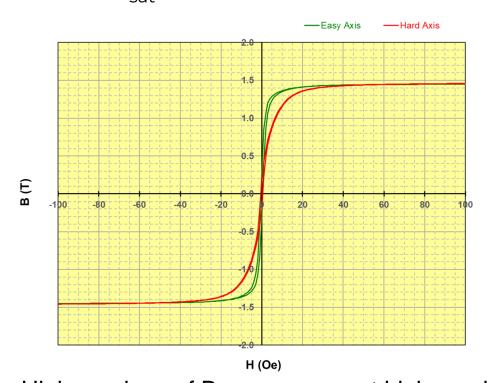

# **High Performance Proprietary ECA Alloy**

EnaChip Alloy (ECA)

- Permeability up to 900

- B<sub>sat</sub>  $\geq$  1.5 T

#### ECA Bias operational range >> NiFe

Higher values of  $B_{USEABLE}$  support higher value of  $B_{DC}$  +  $\Delta B/2$  Higher values of  $\Delta B/2$  enable higher volt-second stress Higher volt-second stress enables higher input voltage buses beyond 12V towards 18V/24V

#### $L_{F\_MAG}$ Vs F (100 kHz – 50 MHz) Scalability By Layers and Thickness

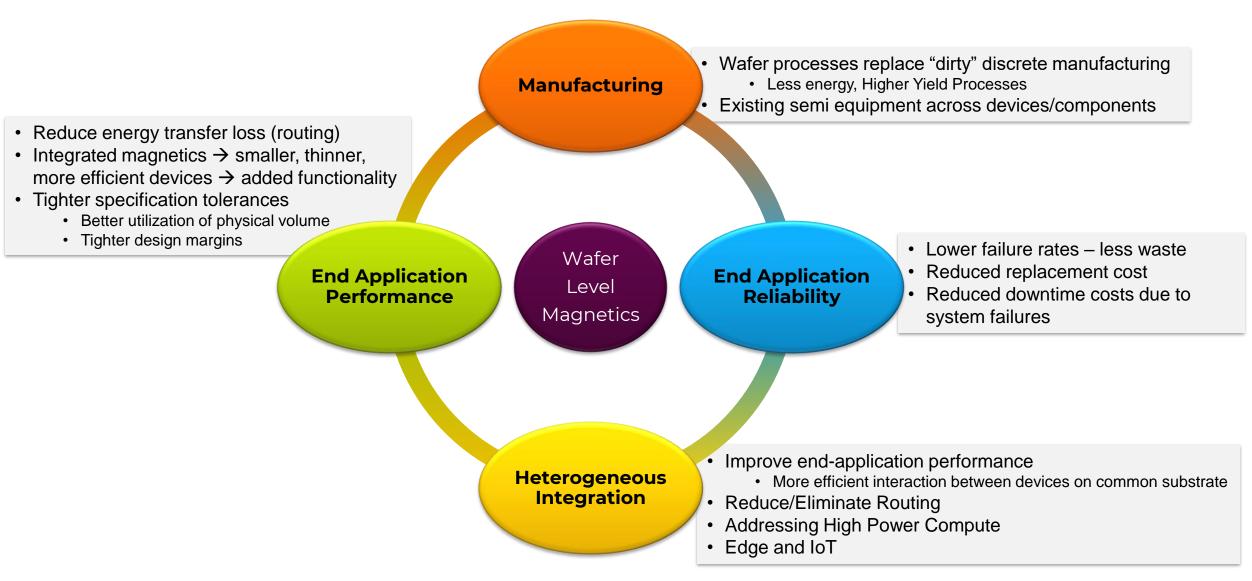

# Wafer Level Magnetics (Impacts on Environmental Sustainability)

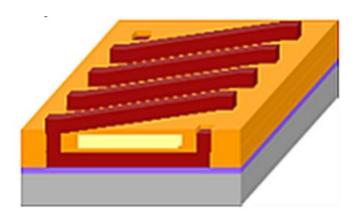

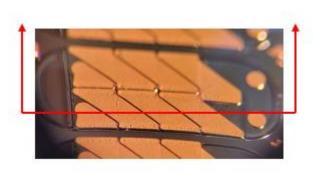

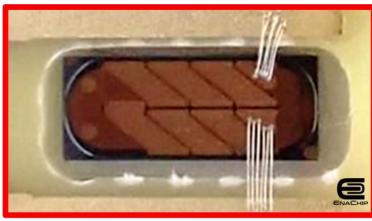

# **Device Examples**

ENACHIP

- Thick Cu toroid micro-inductors

- Multi-core toroids

- Spiral coils

- Electromagnets/Actuators

- Transformers

- Sensors

Inductance density: 100nH/mm<sup>2</sup>

$2nH/m\Omega$

Power Throughput:  $0.5W \le P \le 15W$

Current range:  $0.5A \le I \le 5A$

Operational  $V_{IN}$ :  $1.8 V_{DC} \le V_{IN} \le 18 V_{DC}$ Operational  $V_{OUT}$ :  $0.6 V_{DC} \le V_{OUT} \le 5 V_{DC}$

Working Voltage:  $50 V_{DC}$

Frequency Range:  $5 \text{ MHz} \le f \le 30 \text{ MHz}$ Typical Thickness:  $40 \text{ um} \ge T \le 200 \text{ um}$

3D topography

# Walk away message:

Continuous electroplating of magnetic film and insulator sequentially is a viable technology that **has been demonstrated** at the wafer level

#### That enables:

Single mask thin film magnetic core laminations for high performance wafer level magnetics that support heterogeneous integration

Fast, Low cost, environmentally friendly BEOL – CMOS/GaN compatible simple manufacturing process with existing infrastructure

Wafer level magnetics enables heterogenous integration improving: system technical performance manufacturing and assembly sustainability performance

### Thank you!