CONFIDENTIAL

# High-density Nanoporous silicon decoupling capacitors

Murata Integrated Passive Solutions (MIS)

Mohamed Mehdi Jatlaoui, Ph.D Product Line Manager mohamed.jatlaoui@murata.com

#### **Outline**

- Introduction / Thoughts sharing

- II. Silicon Capacitors: 5W (Where, Who, When, Why, What)

- III. 3D Nanoporous Silicon capacitors for Power applications (PDN, iVR)

- IV. Conclusion

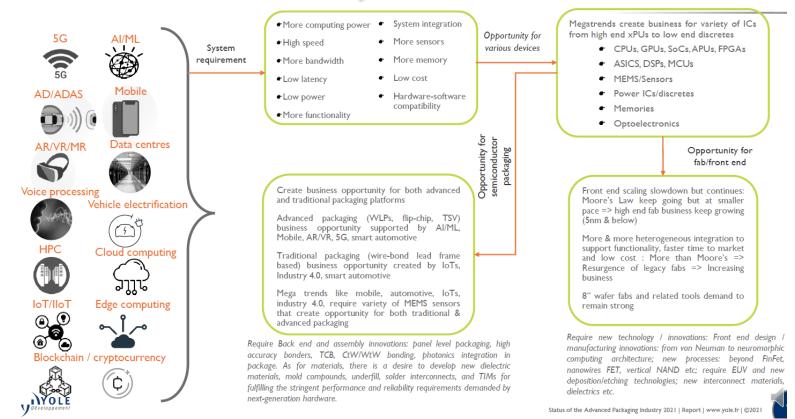

#### I. Introduction

Copyright © Murata Manufacturing Co., Ltd. All rights reserved.

CONFIDENTIAL

Source: Yole Développement

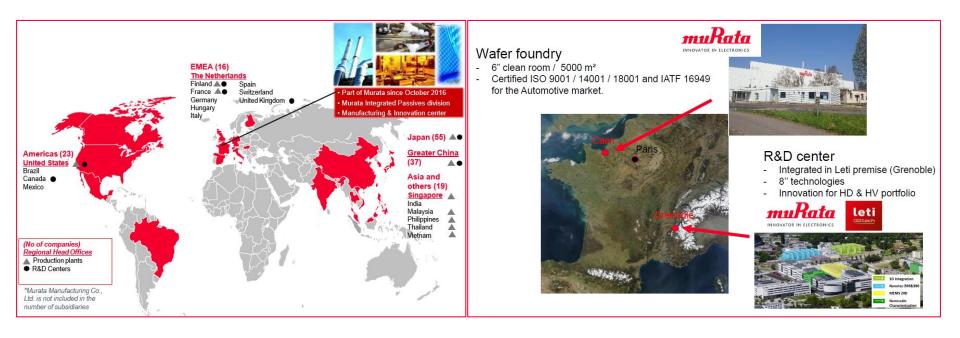

### II. Murata Integrated Passive Solutions\_ Where?

## II. Silicon Capacitors technology\_Who? When?

High Density

**High Capacitance GRM Series** (2.5V~100V, ~220uF)

**Polymer Electrolysis ECAS Series**

(2.5V~25V, ~470uF)

**EDLC** DMF Series (~1000mF, 4,2V)

Low ESL **LLL/LLD Series** (~4.3uF, 9.2uF)

Consumer

Factory Automation, PLC,

Industry

LED lighting, TV, Air conditioner

Smartphone, Tablet, Wearable

(25V~1kV, ~100uF) **Embedded** GRU/LLU Series 🛰 **Implant Class D GCR/GCH Series** (ISO13485)

**High Reliability**

**Ultra Small Size** GRM01/02 Series (008004, 01005)

Non Magnetic MA Series (MRI application )

Imaging Therapy, Hearing Aid, Clinic System Wind / PV Power

**Metal Terminal**

KRM Series

(110um~, Cu VIA Connection)

Healthcare

PA High Q

(250V~500V. 1GHz~10GHz)

Optical Transceiver

**GMA/GMD Series**

(Wire Bonding, Au Electrode)

**GQM Series**

Generation, Oil/Gas System **Energy**

**RDE Series**

Ultra High Voltage **DHS/DHK Series** (DC10~50kV,AC10~25kV)

**High Voltage DHR Series**

**Automotive Grade** GCM Series

(ISO9001, AEC-Q200, TS16949)

Safety Recognized **DE Series**

(13 countries Safety Approved, X2/Y1/Y2)

SNUBBER (SHIZUKI)

MIC-UV Series

(~1.200V, ~1.600uF)

(~1.600V, ~4uF)

**High Power EVC Series**

(~1,600V, ~4uF)

DC-LINK (SHIZUKI) MEC-DL/HV Series

**High Power Conversion**

**Ultra High Voltage, Communication**

Wrong choice of passives can impact and limit the final application

**Miniaturization**

Low profile Low FSI

Low ESR High Reliability Mechanical strength

High Stability

### II. Silicon Capacitors technology\_ Where?

**Optical** transceivers

**UBB**

**DC-DC** Converter 100MHz

High voltage DC-DC Converter SiC /GaN

Medical/Healthcare

**IOT & Communication**

Neurostimulation module

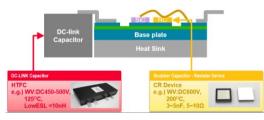

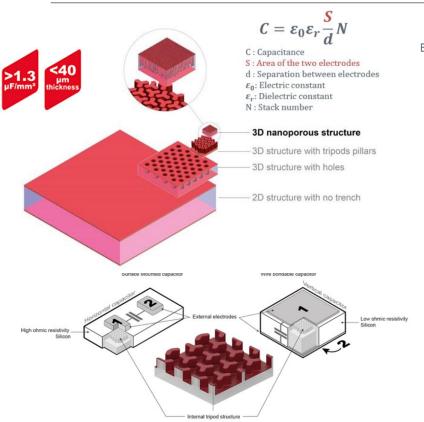

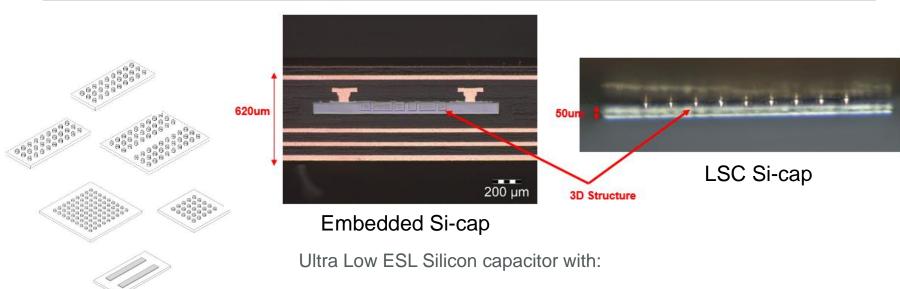

### II. What's Silicon Capacitors Technology?

Murata is committed to a vision of developing innovative integrated Silicon capacitors to match the requirements and trends of SOC

### II. What's Silicon Capacitors Technology?

#### Silicon Capacitors extending MLCC portfolio

### II. What's Silicon Capacitors Technology?

Die Side

Land Side or Embedded

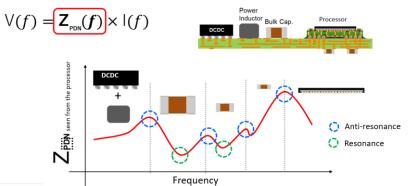

### III. PDN\_di/dt Mitigation

- Workloads exert excessive load transients and instability in the power supply network → variation in CPU activity may cause droop with steep slopes

- The di/dt events of CPUs induces voltage transients that need to be margined for, at the cost of power and performance

- Higher performance cores switch more current, inducing deeper droops. This impact is amplified at lower operating voltages as required by scaling trends

- → There is a need for an efficient PDN decoupling strategy

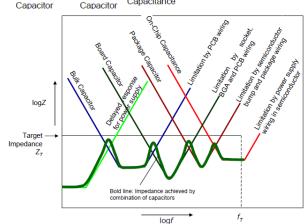

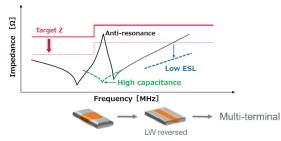

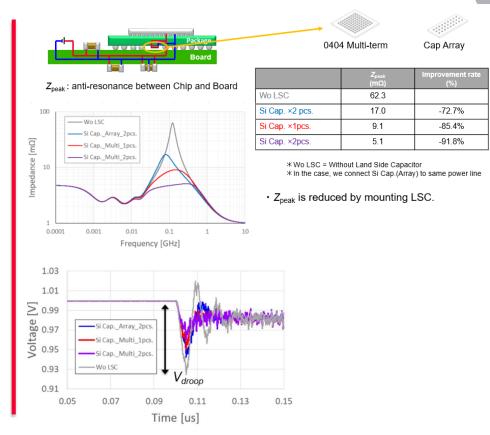

Need to take care of antiresonance and resonance to mitigate voltage noise

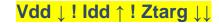

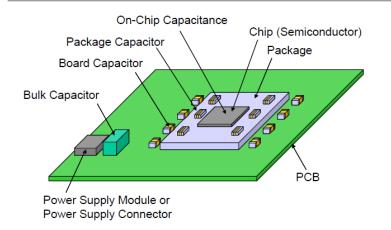

### III. PDN\_Application

- Power supply impedance must be made small over a wide frequency range

- One capacitor cannot achieve the necessary impedance, multiple capacitors are positioned hierarchically to achieve the target power supply impedance

- Due to space constraints, on-chip capacitance is not enough to reduce impedance at high frequencies.

### III. PDN\_Trends and Requirements

#### **Thickness**

#### Low profile capacitor is needed

#### <u>ESL</u>

#### Microfabrication of process

$10~nm \rightarrow 7~nm \rightarrow 5~nm...$

#### Lower target impedance

Low ESL capacitor is needed

#### **General Trends for Mobile & HPC**

- Higher functionality

- Scaling

- Increase in Power density

#### **General requirements for PDN**

- More stability & flat design

- Lower Z design at high frequency

- Lower Z design at anti-resonance

#### **Needs for Capacitors**

- Extreme Low ESL

- Extreme Low profile (Die, Terminal)

- High capacitance

- Adjustable ESR

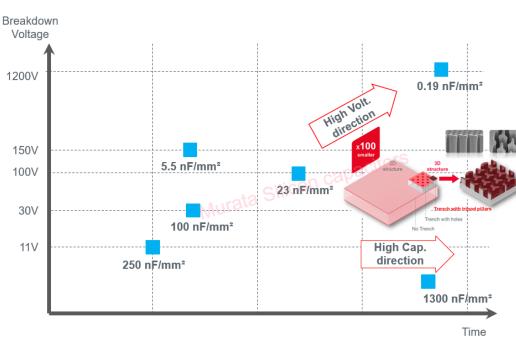

### III. PDN\_Murata's UESL® family solutions

- State of the art density of >1300 nF/mm² in Silicon

- 1 μF in ultra compact 0404 form factor

- Ultra-low ESL (< 5 pH) and ESR (< 5 mΩ)</li>

- < 50 µm thickness

- Mechanical robustness

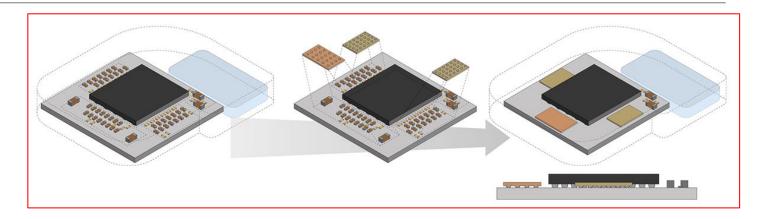

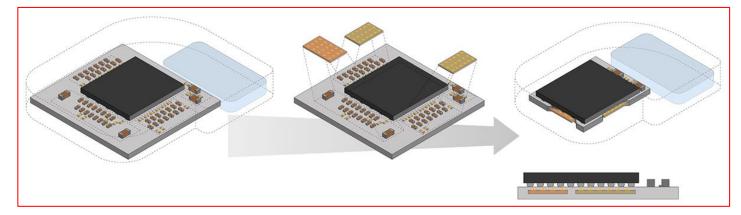

#### III. PDN\_Benefits

#### Si-Caps help reducing ESL

#### Landside packaging

- Si-Caps intrinsic ESL is lower than MLCC

- Assembly ESL (parasitic) is reduced

- Multi-terminals generate smaller current loop → lower ESL (shorter distance between pads)

- Low-profile enables integration closer to IC

#### Embedded packaging

Ability to reduce substrate X/Y size

Source:https://www.murata.com/eneu/products/capacitor/siliconcapacitors/ov erview/medical

| Decoupling cap | Parasitic from assembly               | Cap intrinsic ESL                                     | Conclusion  |

|----------------|---------------------------------------|-------------------------------------------------------|-------------|

| MLCC die-side  | High ESL<br>high distance - Underfill | High ESL                                              | Standard    |

| SiCap embedded | Low ESL<br>close to IC                | Low ESL<br>Multi-terminals<br>Adjacent opposite loops | Improvement |

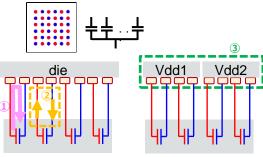

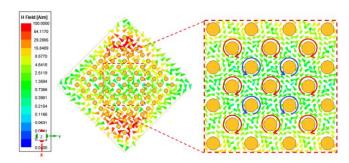

## III. PDN\_Multi-terminal and array structure

Multi-terminal is important to get low ESL.

Array structure offers high flexibility for PDN design

Surface

Current

1GHz

distribution @

Two-terminal Two-terminal die die pin Capacitor + current path current direction -29.6446 24.5935 22.0680 19.5424

Multi-terminal

- Loop decrease(1)

- Counteract electromagnetic wave(2)

- →Low ESL in capacitor Low inductance of wire

Magnetic field distribution @ 1GHz

#### Array structure

- Loop decrease(1)

- Counteract electromagnetic wave(2)

- →Low ESL in capacitor Low inductance in wire

- Capability to connect different power domains(3)

- →Flexibility of AP design

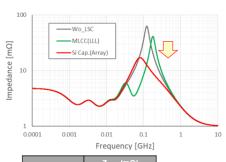

### III. PDN\_Si-caps improve system performance

|                | $Z_{peak}$ (m $\Omega$ ) |          |

|----------------|--------------------------|----------|

| Wo LSC         | 62.7                     |          |

| MLCC(LLL)      | 41.2                     | -24.2 mΩ |

| Si Cap.(Array) | 17.0                     |          |

- Abrupt changes in processor activity induce large current transients in the power delivery network

- There is a need to reduce losses → provide better and more granular regulation to the processor cores

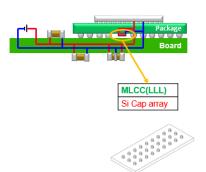

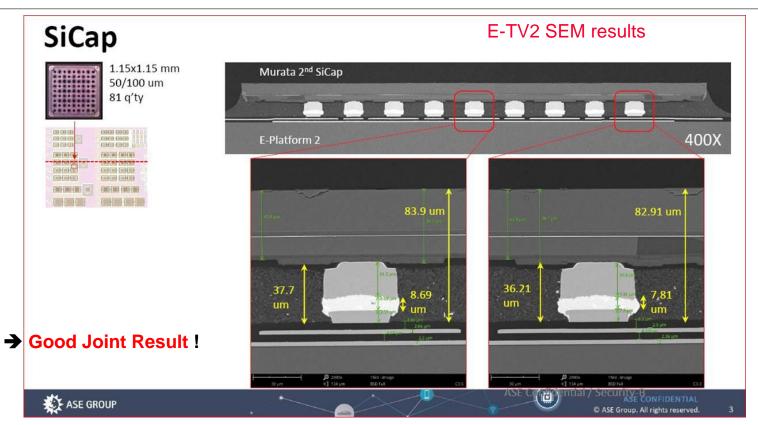

## III. PDN\_Assembly evaluation

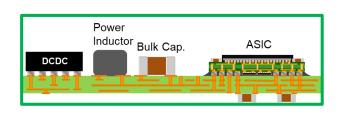

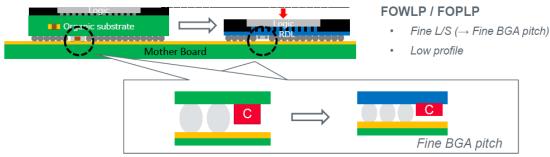

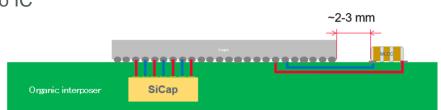

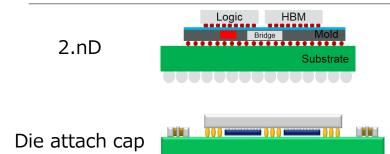

### III. PDN\_Advanced packaging

Power Integrity can be improved using specific cap:

- DC~1MHz Standard (High capacitance)

- 0.1 MHz Multi-terminal (Low inductance)

- 25 MHz Package Cap (Thin and Embedded cap)

- 100s MHz Si Multi-terminal 3D cap

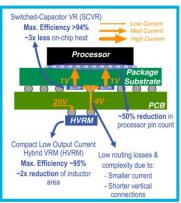

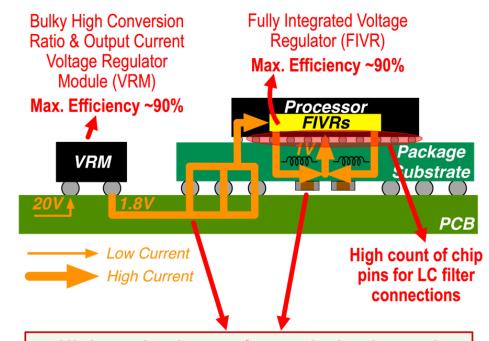

### III. iVR\_Traditional Power Delivery

Prof. Hanh-Phuc Le and his team

- High routing losses & complexity due to the lateral distribution of very high currents

- Overall System Efficiency ~80%

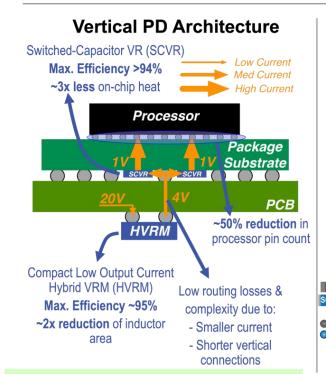

#### III. iVR\_ Approach based on Two-Stage Vertical PD and Management with Heterogeneous 3D Implementation

- ~2x reduction in package PDM pins

- 4x interconnect loss reduction:

- ~1.5x increase in available data IO pins.

#### **Confidential – Unpublished materials!**

Global Research Collaboration

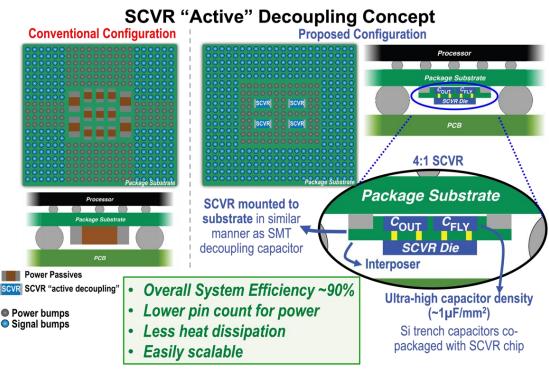

### III. iVR\_ New Approach

### UC San Diego

Prof. Hanh-Phuc Le and his team

**Unpublished Materials** Will be published at ISSCC Feb. 2023

**Confidential – Unpublished materials!**

- New circuit topology and control

- Switched capacitor for the last stage

- Integrated passive devices (IPDs)

- $>1 uF/mm^2$

- Silicon interposer for packaging

- Target: 2 A/mm<sup>2</sup>

- 87% total efficiency, with 94% for HVRM and ~93% for SCVR

- Accepted to ISSCC 2023

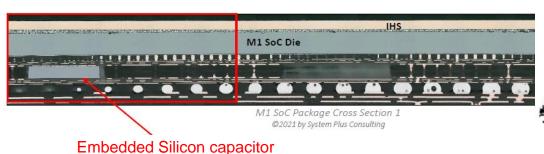

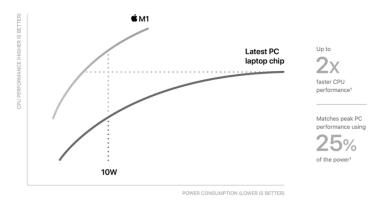

### VI. Conclusion\_On-package Si-cap for CPU

Source: https://www.apple.com/fr/newsroom/2020/11/apple-unleashes-m1/

#### 4 Land Side + 6 Embedded Silicon capacitors

Source: SystemPlus consulting

#### CPU performance vs. power

DRAM memory

M1 Processor Die

M2 Processor Die

SYSTEMPlus

Bottom Package

Silicon Capacitor

Silicon Capacitor

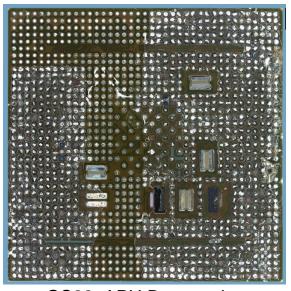

### VI. Conclusion\_ On package Si-cap for APU

GS22\_APU Bottom view

Source: SYSTEMPlus

Silicon capacitors → enabling innovation and push the limits

#### Thanks a lot for your time and attention!

Contact: mohamed.jatlaoui@murata.com